使用 Synopsys 和 Cadence 工具的 ASIC 设计流程 (Temporarily Stop Updating)

第01章 简介

本教程介绍了如何使用 Synopsys 和 Cadence 提供的 ASIC 工具,将 RTL(寄存器传输级)设计映射到标准单元库,并最终实现硅片制造的完整流程。它不仅涵盖了综合(Synthesis)、布局布线(Place-and-Route)、仿真(Simulation)和功耗分析(Power Analysis)等主要环节,还深入讲解了相关工具的使用方法。

通过本教程,学生需要手动执行每一步操作,以了解每个环节背后的详细步骤和原理。这种方式不仅能加深对ASIC设计流程的理解,还为后续的自动化流程奠定了基础。

请注意,本教程的前提是学生已经完成了Linux、Git以及Verilog的相关基础教程。

教程主要使用以下五个核心工具:

- PyMTL:用于RTL建模、测试和验证。

- Synopsys VCS:支持4状态RTL和门级仿真。

- Synopsys Design Compiler (DC):将RTL代码转换为门级网表。

- Cadence Innovus:执行布局布线,生成完整的物理设计。

- Synopsys PrimeTime (PT):进行功耗分析。

此外,还使用了一些辅助工具:

- vcd2saif:用于从仿真生成的波形文件中提取网络活动因子。

- Klayout:用于可视化查看最终的物理布局文件(.gds格式)。

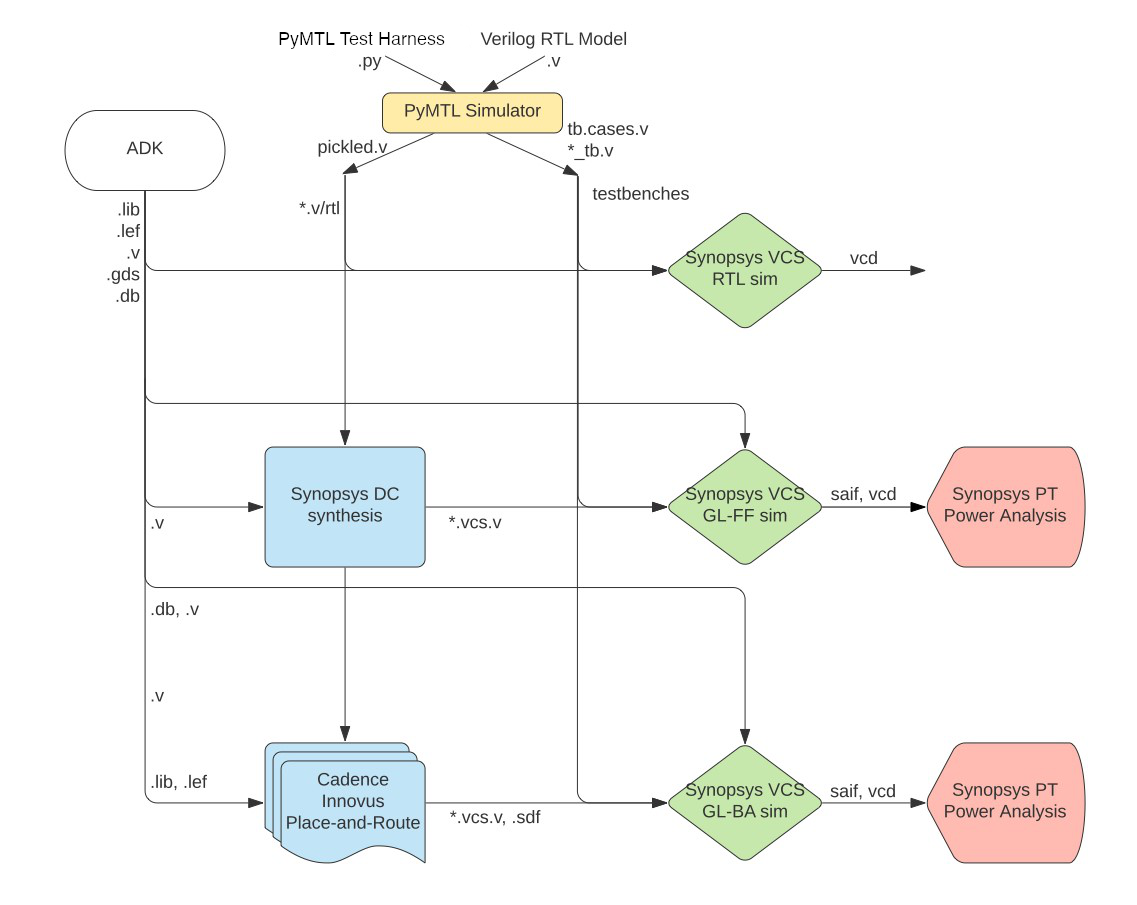

下方的流程图详细展示了每个工具之间的数据流关系:

- 输入数据包括标准单元库的多个视图文件(.lib、.lef、.db等)和设计的 Verilog RTL 模型。

- 输出数据覆盖门级网表(.v)、仿真波形文件(.vcd)、寄生参数文件(.spef)、功耗数据文件(.saif)、最终布局文件(.gds)等。

每个工具依次接收和生成这些文件,形成一个完整的ASIC设计流程。具体地:

我们使用Verilog语言编写RTL模型,并使用PyMTL框架进行测试、验证和性能评估(以周期为单位计算执行时间)。这部分流程与ECE 4750课程中使用的流程非常相似。在确认设计能够正确工作之后,我们会开始将设计推向完整的流程。

我们使用Synopsys VCS工具编译并运行4态RTL和门级仿真。这些仿真帮助我们在流程的不同阶段建立对设计的信心。从这些仿真中,我们可以生成

.vcd(Verilog Change Dump)格式的波形文件,并使用vcd2saif工具将这些波形文件转换为每个网络的平均活动因子,存储在.saif文件中。这些活动因子将被用于功耗分析。门级仿真是一个重要工具,可以确保在综合和优化过程中没有出现影响设计正确性的情况,并且相比于RTL仿真,门级仿真可以提供更准确的功耗分析。同时,尽管静态时序分析(STA)会分析所有路径,门级仿真(GL simulation)也可以作为备选工具,检查是否存在保持时间和建立时间违规(芯片设计师必须保持警惕!)。我们使用Synopsys Design Compiler (DC)对设计进行综合,这意味着将Verilog RTL模型转换为基于标准单元库的门级网表。综合需要提供标准单元库的抽象逻辑和时序视图(

.db格式)。除了生成Verilog门级网表,Synopsys DC还可以生成一个包含门级网表和时序信息的.ddc文件,该文件可以通过Synopsys Design Vision (DV)工具进行检查。我们使用Cadence Innovus对设计进行布局布线。这意味着需要将门级网表中的所有门放置到芯片上的行中,并生成连接所有门的金属布线。我们需要向Cadence Innovus提供与Synopsys DC相同的抽象逻辑和时序视图,同时还需提供技术信息文件(

.lef和.captable格式)以及标准单元库的抽象物理视图(同样为.lef格式)。Cadence Innovus会生成更新的Verilog门级网表,一个包含所有网络寄生电阻/电容信息的.spef文件,以及一个包含最终布局的.gds文件。.gds文件可以通过开源工具Klayout GDS查看器进行检查。Cadence Innovus还会生成报告,用于精确描述芯片的面积和时序特性。我们使用Synopsys PrimeTime (PT)对设计进行功耗分析。我们需要向Synopsys PT提供与Synopsys DC和Cadence Innovus相同的抽象逻辑、时序和功耗视图。此外,还需要提供设计中每个网络的切换活动信息(来自

.saif文件)和电容信息(来自.spef文件)。Synopsys PT将切换活动、电容、时钟频率和电压结合起来,估算每个网络以及整个模块的功耗。这些估算结果将以各种报告的形式呈现出来。

可以从以下的折叠卡中得到各工具的信息:

[PyMTL 测试与验证]

- RTL 建模

在流程的初始阶段,我们使用 PyMTL 框架对 RTL 模型进行建模和验证。PyMTL 提供了一种高效的方式来测试设计是否按照预期运行,并评估设计的性能(例如运行所需的时钟周期数)。

- 测试平台

PyMTL 会将 RTL 模型转换为标准的 Verilog 文件(.v格式)。这些文件将被用于后续的综合和仿真流程。与 PyMTL 一起工作的还有测试平台,它会生成相关的测试输入和预期输出,用于验证设计的正确性。

[Synopsys VCS 仿真]

- RTL 仿真

使用 Synopsys VCS 工具对生成的 Verilog RTL 文件运行 4 状态仿真。仿真会生成一个 .vcd(Verilog Change Dump)格式的波形文件,记录了设计中每个信号的活动变化。

- 活动因子提取

通过 vcd2saif 工具,将 .vcd 文件转换为 .saif 文件。.saif 文件包含了每个网络的平均活动因子,这些因子会被用作功耗分析的输入数据。

- 门级仿真

综合完成后,还需要使用 VCS 对生成的门级网表进行仿真,验证其功能是否与原始 RTL 设计一致。门级仿真还能检测设计是否存在时序违规(例如保持时间或建立时间的违例)。

[Synopsys Design Compiler 综合]

- 综合目标

Synopsys Design Compiler (DC) 的作用是将 RTL 模型(描述逻辑功能)转化为基于标准单元库的门级网表。网表中的每个逻辑门都来源于标准单元库。

- 标准单元库

标准单元库提供了:

- 逻辑视图:描述逻辑门的功能。

- 时序视图:定义门的延迟。

- 物理视图:用于布局布线的物理尺寸。

这些信息通常以 .db 格式提供给 DC 工具。

- 综合结果

综合后,DC 工具会生成:

- 门级网表(.v):逻辑门及其连接的描述。

- 时序信息(.ddc):门级网表的时序数据。

这些结果可以通过 Synopsys Design Vision 工具进一步检查。

[Cadence Innovus 布局布线]

- 工具功能

Cadence Innovus 用于执行布局布线,即将门级网表中的逻辑门放置在芯片上并连接这些逻辑门。

- 输入数据

布局布线需要以下输入:

- 逻辑与时序视图(来自 .db 文件)。

- 物理视图与技术信息(.lef 和 .captable 文件)。

- 门级网表(来自综合)。

- 输出数据

布局布线完成后,Innovus 会生成:

- 更新后的门级网表(.v):反映实际布局的网表。

- 寄生参数文件(.spef):包含电阻和电容信息。

- 物理布局文件(.gds):描述芯片的最终布局。

这些文件可以通过工具(如 Klayout)进行可视化。

[Synopsys PrimeTime 功耗分析]

- 输入数据

Synopsys PrimeTime (PT) 使用以下数据进行功耗计算:

- 逻辑、时序、功耗视图(来自标准单元库)。

- 活动因子数据(.saif 文件)。

- 寄生参数数据(.spef 文件)。

- 计算过程

PT 将活动因子、电容、时钟频率和电压结合起来,估算每个网络和模块的功耗。这些结果会被写入详细的功耗报告中。

Synopsys 和 Cadence 为这些 ASIC 工具提供了大量文档。这是 整理文档得到的公共课程网页内容。

以下是配置环境和克隆项目所需的命令:

1 | source setup-ece5745.sh |

第02章 Nangate 45nm 标准单元库

在访问标准单元库之前,您需要访问“物理设计套件”(PDK)。PDK 包含针对特定技术的全定制电路设计所需的所有设计文件。因此,这将包括设计规则手册以及晶体管和其他设备的 SPICE 电路模型。获取真正的 PDK 很困难。它需要与代工厂协商并签署多项保密协议。因此,在本课程中,我们将使用 FreePDK45 PDK 。

这是一种为研究和教学目的设计的“虚拟”45nm工艺技术。尽管这种 PDK 不能用于流片,但其技术特性足够代表性,能够提供合理的面积、能量和时序估算。FreePDK45 PDK 安装路径:

1 | % cd $ADK_PKGS/freepdk-45nm/pkgs/FreePDK45-1.4 |

标准单元设计人员将使用 PDK 来实现标准单元库。标准单元库是遵循一组标准化的逻辑、电气和物理策略的组合和顺序逻辑门的集合。例如,所有标准单元通常都具有相同的高度,包括与预定的垂直和水平网格对齐的引脚,包括位于预定位置的电源/接地轨和 nwell,并支持预定数量的驱动强度。标准单元设计人员通常会为每个逻辑门创建高级行为规范(以 Verilog 格式)、电路原理图(以 SPICE 格式)和实际布局(以.gds格式)。Synopsys 和 Cadence 工具实际上并不使用这些低级实现,因为它们实际上太详细了。相反,这些工具使用标准单元的抽象视图,这些视图以更高的级别捕获逻辑功能、时序、几何形状和功耗。

就像 PDK 一样,获取真正的标准单元库的访问权限也很困难。首先需要获取 PDK 的访问权限,然后与制造标准单元的公司进行协商,通常还要签署更多保密协议。在本课程中,我们将使用基于开放的 FreePDK45 PDK 的 Nangate 45nm 标准单元库。

Nangate 是一家开发自动生成标准单元库工具的公司,因此他们公开了这个库,以此来展示他们的工具。由于它是一个开放库,因此它是研究和教学的绝佳资源。尽管标准单元库基于“假” 45nm PDK,但该库提供了对真正的 45nm 技术中真正的商业标准库的非常合理的估计。在本节中,我们将介绍 Nangate 标准单元库的低级实现和高级视图。

标准单元库发行版可以包含数千个文件中的 GB 级数据。例如,以下是 Nangate 标准单元库的发行版。

1 | % cd $ADK_PKGS/freepdk-45nm/pkgs/NangateOpenCellLibrary_PDKv1_3_v2010_12 |

标准单元库的设计包括以下内容:

- 高级行为描述(Verilog 实现)。

- 电路原理图(SPICE 实现)。

- 实际布局文件(

.gds格式)。

尽管标准单元库的低级实现非常详细,但 Synopsys 和 Cadence 工具主要使用更高抽象层次的视图,例如:

- 逻辑视图:逻辑功能描述。

- 时序视图:门延迟和相关特性。

- 几何视图:单元的物理尺寸和布局。

- 功耗视图:功耗和漏电流特性。

为了简化本课程中 Nangate 标准单元库的使用,我们创建了一组小得多的明确定义的符号链接,这些符号链接仅指向我们想要在本课程中使用的关键文件。我们将这组符号链接称为“ASIC 设计套件”(ADK)。以下是包含这些符号链接的目录。

1 | % cd $ECE5745_STDCELLS |

接下来可以简单看一下标准单元设计的层次视图。

- 电路原理图

以下是 NAND3_X1(3 输入 NAND 门)的 SPICE 原理图:

1 | % less -p NAND3_X1 $ECE5745_STDCELLS/stdcells.spi |

本质上,该原理图包括三个串联排列在下拉网络中的 NMOS 晶体管和三个并联排列在上拉网络中的 PMOS 晶体管。PMOS 晶体管比 NMOS 晶体管大(见W=参数),因为空穴的迁移率小于电子的迁移率。

- 物理布局

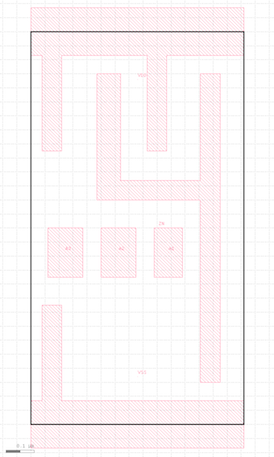

接下来可以使用 Klayout GDS 查看器查看布局:

1 | klayout -l $ECE5745_STDCELLS/klayout.lyp $ECE5745_STDCELLS/stdcells.gds |

请注意,我们使用的.lyp文件是预定义的层配色方案,可以更轻松地查看 GDS 文件。要查看 3 输入 NAND 单元,请在左侧单元列表中找到 NAND3 X1 单元,然后从菜单中选择 _Display > Show as New Top。以下是此单元的布局图片。

其中:

- 绿色:扩散区;

- 红色:多晶硅;

- 蓝色:金属层(M1);

- 灰色:nwell 区域。

标准单元的电源轨和地轨位于顶部和底部,确保单元在行排列时通过对接方式连接。

- Verilog 行为描述

以下是 NAND3_X1 的 Verilog 实现:

1 | % less -p NAND3_X1 $ECE5745_STDCELLS/stdcells.v |

该实现使用 Verilog 基本门单元(如 not 和 and),并包含时序延迟的 specify 块。

- 带寄生参数的电路模型

通过工具提取寄生电阻和电容值,可生成更详细的 SPICE 电路模型:

1 | % less -p NAND3_X1 $ECE5745_STDCELLS/stdcells-lpe.spi |

它的完整模型甚至有有几百行,但实际上 ASIC 工具实际上不需要这么多细节。我们可以使用一组特殊的工具来创建适合 ASIC 工具使用的更高级别的电路时序和功率抽象视图。本质上,这些工具运行许多电路级模拟来创建存储在.lib(Liberty) 文件中的特性数据。

.lib文件

.lib 文件是标准单元的高抽象视图,包含逻辑、时序和功耗特性:

1 | % less -p NAND3_X1 $ECE5745_STDCELLS/stdcells.lib |

这只是该单元 .lib 文件中包含信息的一小部分。我们将在课程的后续部分中详细讨论这种 .lib 文件的具体内容。从中可以看出,.lib 文件包含了关于面积、泄漏功耗、每个输入引脚的电容、逻辑功能和时序等信息。所有数据的单位都在 .lib 文件的顶部定义。在这个片段中,你可以看到该单元的面积为 1.064 平方微米,泄漏功耗为 18.1 纳瓦。输入引脚 A1 的电容为 1.59 飞法,尽管文件中还有其他数据记录了输入信号上升或下降时电容的变化情况。输出引脚 ZN 实现了逻辑表达式 !((A1 & A2) & A3)(即一个三输入 NAND 门)。.lib 文件中的数据通常通过一维或二维查找表(即值表)进行表示。在上述片段中可以看到两个这样的查找表。

其中:

第一张表:延迟(Delay)

- 功能:记录输入引脚 A1 到输出引脚 ZN 的延迟值,该延迟取决于两个参数:

- 输入信号转换时间(表格水平方向)。

- 负载电容(表格垂直方向)。

延迟场景:此表描述的是 ZN 从高到低(falling)的延迟。对于 ZN 从低到高(rising)的延迟,以及其他输入引脚的延迟,有对应的其他表格。

特点:

- 输入信号转换时间越长、驱动的负载越大,逻辑门的延迟会越长。

- 表格中的每个数据点都基于一次或多次详细的电路级仿真。

示例:当输入转换速率为 4.7ps,输出负载为 1.82fF 时,输入引脚 A1 到输出引脚 ZN 的延迟为 16ps。

用途:这种细节水平的数据可以用于非常精确的静态时序分析(Static Timing Analysis, STA)。

第二张表:内部功耗(Internal Power)

- 功能:记录逻辑门本身的功耗(不包括输出负载消耗),其数据依赖于:

- 输入信号转换时间(表格水平方向)。

- 负载电容(表格垂直方向)。

- 计算方式:

- 表格中的每个数据点来源于详细的 SPICE 仿真。

- 功耗计算方法为:从电源供电中测量总电流,再减去用于输出负载充电的电流。

- 公式含义:未用于输出负载充电的能量即为内部能量。

- 注意事项:

- 内部功耗有时会出现负值。这是因为不同能量统计方法的结果不同:

- 假设能量仅在输出节点充电时消耗,放电时不消耗能量。

- 假设输出充电和放电各消耗一半能量,此时可能会看到负值。

关于 .lib 文件和 .db 文件

.lib 文件:

- 包含标准单元库的抽象逻辑、时序和功耗信息。

- 不包括标准单元的物理信息。

.db 文件:

- 是

.lib文件的二进制预编译版本。

优势:

文件体积更小。

便于 ASIC 工具使用。

尽管 ASIC 工具可以直接使用

.gds文件,但它们实际上并不需要那么详细的信息。使用特殊工具生成

.lef文件,它是单元物理属性的高抽象视图,适合 ASIC 工具处理。

LEF 文件(抽象物理视图)

- 功能:描述单元的边界、引脚位置和阻塞区域。

- 内容:

- 单元的尺寸信息。

- 电源和地引脚的位置与形状。

- 阻塞区域(如某些金属层的使用限制)。

- 应用:

- 用于布局布线工具简化物理设计过程。

- 示例:可以使用工具查看 LEF 文件,了解单元的抽象物理布局。

.lef文件

.lef 文件为单元的物理布局提供高层次视图:

1 | % less -p NAND3_X1 $ECE5745_STDCELLS/stdcells.lef |

这只是文件中包含的有关此单元的信息的一小部分.lef 。您可以看到.lef文件包含有关单元尺寸以及电源/接地和信号引脚的位置和尺寸的信息。文件还包括有关“障碍物”(或阻塞)的信息等。这些是单元区域,不应由 ASIC 工具使用。例如,如果单元需要使用金属 2 (M2),它将在 M2 上产生阻塞,以便 ASIC 工具知道不要在该区域布线任何 M2 线。您也可以使用 Klayout 查看.lef文件。

1 | % klayout |

从menu中选择File > Import > LEF,导航到文件stdcells.lef。这是其图片:

如果将 .lef 文件与 .gds 文件进行比较,可以发现 .lef 文件是一种更简单的表示形式,它仅包含单元的边界、引脚和阻塞区域的信息。

标准单元库还包括几个文件(例如 rtk-tech.tf, rtk-tech.lef, rtk-typical.captable),用于捕获有关金属互连的信息,包括线宽、间距和寄生效应。例如,让我们看一下文件 .captable

1 | % less -p M1 $ECE5745_STDCELLS/rtk-typical.captable |

该文件包含有关 M1 上导线的最小尺寸以及这些导线的电阻的信息。它还包含一个导线电容表,其中不同行代表不同的导线宽度和间距。ASIC 工具可以使用此类技术信息来优化和分析。

最后,标准单元库始终会包含一个数据手册,它是一份描述库中每个单元详细信息的文档。可以花几分钟时间浏览位于以下类 Canvas 页面上的 Nangate 标准单元库数据手册 。

- Title: 使用 Synopsys 和 Cadence 工具的 ASIC 设计流程 (Temporarily Stop Updating)

- Author: Albert Cheung

- Created at : 2024-12-04 19:59:06

- Updated at : 2025-02-18 21:40:36

- Link: https://www.albertc9.github.io/2024/12/04/introduction-to-asic-design/

- License: This work is licensed under CC BY-NC-SA 4.0.